XCV200-6FG456C FPGA: Ciri, Spesifikasi, Pengaturcaraan, dan Aplikasi

XCV200-6FG456C adalah FPGA yang kuat (Array Gate Programmable Field) dari siri AMD Xilinx Virtex®.Panduan ini menerangkan ciri -cirinya, susun atur pin, langkah pengaturcaraan, dan kegunaan.Dengan kuasa pemprosesan yang tinggi, pilihan reka bentuk fleksibel, dan keupayaan input/output (I/O) yang kuat, FPGA ini membantu membina sistem digital yang cepat dan boleh dipercayai.Sama ada anda sedang menjalankan rangkaian, sistem kawalan, atau elektronik tersuai, panduan ini akan membantu anda memahami bagaimana XCV200-6FG456C boleh digunakan dalam projek anda.Katalog

Gambaran keseluruhan XCV200-6FG456C

The XCV200-6FG456C adalah model yang ketara dalam keluarga FPGA AMD Xilinx Virtex®, yang direka untuk menyediakan penyelesaian logik yang dapat diprogramkan yang mantap untuk sistem digital yang kompleks.Cip spesifik ini merangkumi kira -kira 236,666 pintu gerbang dan mempunyai 1,176 blok logik yang boleh dikonfigurasikan (CLBS) dan 5,292 sel logik.Ia juga termasuk 57,344 jumlah bit RAM dan menyokong 284 I/O pin, ditempatkan dalam pakej Grid Grid (FBGA) 456-ball, berukuran 23mm x 23mm.Model ini beroperasi pada voltan nominal 2.5V, dengan julat 2.375V hingga 2.625V, dan boleh berfungsi dalam julat suhu 0 ° C hingga 85 ° C.Siri Virtex® yang lebih luas memenuhi pelbagai aplikasi dengan kepadatan dari 50,000 hingga lebih 1 juta pintu gerbang sistem dan kadar jam sistem sehingga 200 MHz.Ia menyokong banyak piawaian I/O termasuk LVTTL, LVCMOS, dan PCI, antara lain.Ciri-ciri seperti gelung terkunci kelewatan (DLL), blok logik yang boleh dikonfigurasikan dengan memori tertanam, dan logik membawa khusus untuk operasi aritmetik meningkatkan fungsinya.Dikeluarkan menggunakan proses logam 0.22 μm 5-lapisan, keluarga Virtex® menjamin prestasi dan kebolehpercayaan.

Jika anda ingin mengintegrasikan teknologi FPGA peringkat atas ke dalam produk atau sistem anda, membeli XCV200-6FG456C secara pukal dengan kami adalah langkah pintar.Ia memenuhi piawaian industri dan membuat anda lebih awal daripada keperluan teknologi masa depan.

Ciri-ciri XCV200-6FG456C

• Pintu gerbang: XCV200-6FG456C menawarkan kira-kira 236,666 pintu sistem.Kiraan pintu tinggi ini membolehkan pelaksanaan litar logik digital bersepadu kompleks pada cip tunggal, meningkatkan prestasi dan fleksibiliti dalam pelbagai aplikasi.

• Sumber logik: Ia termasuk 1,176 blok logik yang boleh dikonfigurasikan (CLBS) dan 5,292 sel logik.Sumber -sumber ini adalah baik untuk mereka bentuk litar digital yang fleksibel dan berskala.CLBS boleh diprogramkan untuk melaksanakan pelbagai fungsi logik, sementara banyak sel logik membolehkan pengendalian operasi dan proses logik yang luas.

• Ingatan: Peranti ini menyediakan 57,344 bit RAM, diedarkan di antara blok logiknya.RAM terbenam ini digunakan untuk aplikasi yang memerlukan penyimpanan dan pengambilan data yang cepat dan cekap, menyokong operasi data berkelajuan tinggi yang penting untuk sistem digital moden.

• Keupayaan I/O.: Dengan 284 pin input/output, XCV200-6FG456C memudahkan keupayaan interfacing yang luas.Pin I/O ini menyokong pelbagai piawaian isyarat dan membolehkan FPGA berkomunikasi dengan berkesan dengan komponen lain dalam sistem, seperti peranti memori, pemproses, dan periferal.

• Julat voltan dan suhu: Beroperasi pada voltan nominal 2.5V, dengan julat yang boleh diterima dari 2.375V hingga 2.625V, FPGA ini direka untuk penggunaan kuasa rendah sambil mengekalkan prestasi yang mantap.Ia boleh beroperasi dalam julat suhu persimpangan 0 ° C hingga 85 ° C, memastikan kebolehpercayaan di bawah pelbagai keadaan persekitaran.

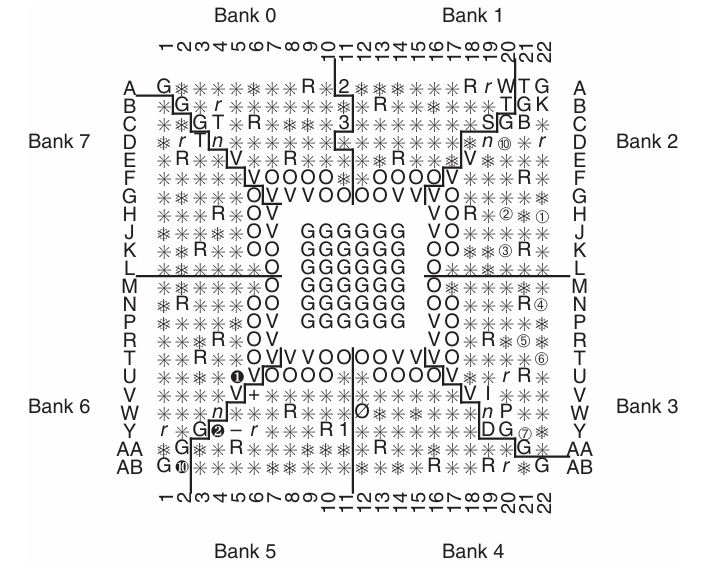

Rajah fungsi pin xcv200-6fg456c pin

The Rajah fungsi pin xcv200-6fg456c pin adalah perwakilan berstruktur dari tugasan pin FPGA, dikategorikan ke bank yang berbeza (Bank 0 ke Bank 7).Setiap kumpulan bank pin berdasarkan fungsi dan penempatan fizikal mereka pada pakej FPGA.Sistem penomboran dan pelabelan mengikuti corak grid di mana baris dilambangkan oleh huruf (a, b, c, dll), dan lajur mengikut nombor (1, 2, 3, dll), yang memudahkan pengenalan cepat pin tertentu.Bank -bank ini sesuai dengan fungsi input/output yang berlainan, kuasa, tanah, dan penghalaan isyarat khusus.PIN diberikan pelbagai kumpulan berfungsi, termasuk tujuan umum I/O (GPIO), sering dilabelkan sebagai "G" (input/output umum), "V" (bekalan voltan), dan "O" (output).Kuasa dan pin tanah ditandakan dengan jelas, memastikan operasi FPGA yang stabil.Pin tujuan khas seperti input jam, semula, dan isyarat kawalan dikenal pasti dengan simbol seperti "R" atau "T."Sesetengah pin juga melayani peranan komunikasi khusus, termasuk konfigurasi JTAG dan kelajuan tinggi, untuk pengaturcaraan dan debugging.

XCV200-6FG456C Rajah blok

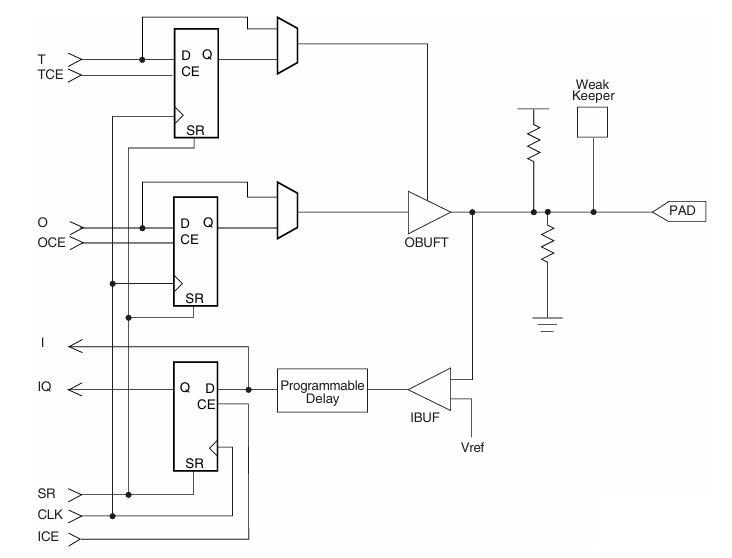

Blok input/output

Rajah mewakili Blok input/output (IOB) Struktur XCV200-6FG456C FPGA, yang merupakan ahli keluarga Xilinx Virtex.Rajah ini mempamerkan elemen utama yang terlibat dalam operasi input dan output, menonjolkan mekanisme aliran data dan kawalan.Pada teras gambarajah, tiga flop flop digunakan untuk mendaftarkan isyarat untuk input, output, dan kawalan tri-state.Daftar output dikawal oleh isyarat OCE (Output Clock Enable), yang menentukan apabila data output dilekatkan.Begitu juga, daftar Tri-State dikawal oleh TCE (Tri-State Clock Enable), membolehkan atau melumpuhkan penampan output.Daftar input menangkap data masuk dan menggunakan kelewatan yang boleh diprogramkan sebelum menyampaikannya ke logik FPGA dalaman melalui IBUF (penampan input).Obuft (penampan output tri-negeri) memastikan bahawa FPGA boleh memacu isyarat ke pad (I/O pin) atau meletakkannya dalam keadaan impedans tinggi, bergantung kepada logik kawalan.Litar penjaga yang lemah dimasukkan ke dalam pad untuk mengekalkan keadaan logik terakhir yang diketahui apabila tiada pemandu aktif hadir, menghalang keadaan terapung yang tidak diingini.Voltan rujukan (VREF) digunakan untuk piawaian input tertentu, seperti SSTL atau HSTL, yang memerlukan tahap voltan yang tepat untuk operasi yang betul.Secara keseluruhannya, struktur IOB ini membolehkan FPGA menguruskan penghantaran data berkelajuan tinggi, menyokong piawaian I/O yang berbeza, dan memberikan kawalan fleksibel ke atas masa isyarat dan integriti.

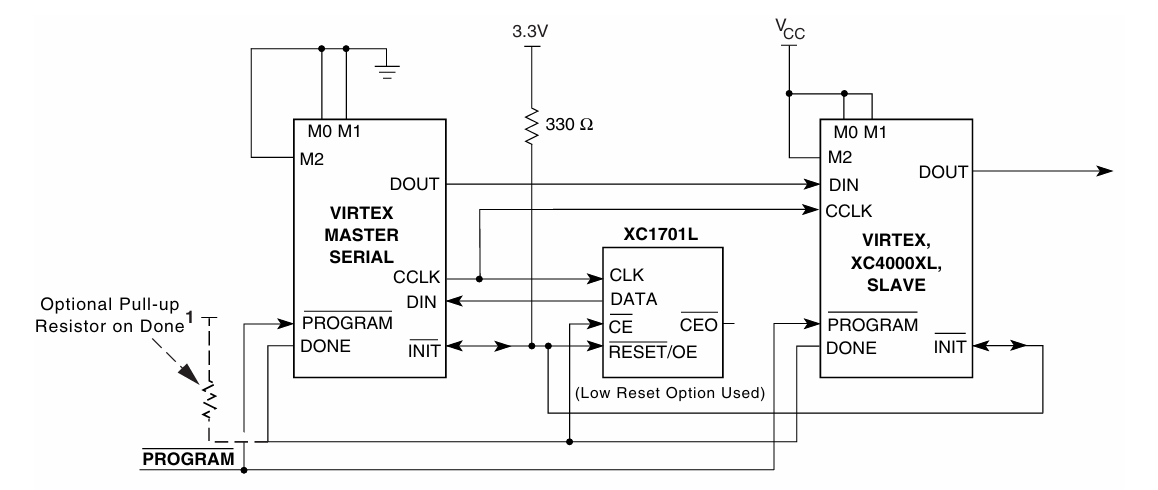

Mod Serial Sarjana/Hamba

The Mod Serial Sarjana/Hamba Rajah blok menggambarkan proses konfigurasi Virtex FPGA, khususnya XCV200-6FG456C, apabila diprogramkan dalam konfigurasi rantai daisy menggunakan EEPROM bersiri (XC1701L).Dalam persediaan ini, satu peranti Virtex beroperasi sebagai tuan, mengawal jam konfigurasi (CCLK) dan menyebarkan data konfigurasi secara serentak ke FPGA hamba tambahan dalam rantai.Master FPGA memulakan proses konfigurasi dengan menegaskan isyarat program, menetapkan semula semua peranti dalam rantai.Sebaik sahaja permulaan selesai, isyarat INIT menunjukkan kesediaan, dan data konfigurasi mengalir dari EEPROM bersiri (XC1701L) ke pin DIN (data dalam) FPGA induk.Master FPGA membaca data dari EEPROM dan meneruskannya melalui DOUT (data keluar) kepada FPGA hamba berikutnya, menyegerakkan pemindahan data menggunakan isyarat CCLK.Isyarat yang dilakukan digunakan untuk menunjukkan konfigurasi yang berjaya, dengan perintang pull-up pilihan memastikan keadaan tinggi yang stabil apabila konfigurasi selesai.EEPROM XC1701L dikawal oleh Master FPGA menggunakan CLK, DATA, CE (CHIP enable), dan RESET/OE (Output Enable), memastikan data konfigurasi yang disimpan diambil dengan betul.Kaedah konfigurasi ini adalah cekap untuk pengaturcaraan pelbagai FPGA menggunakan satu EEPROM tunggal, mengurangkan kerumitan pendawaian luaran dan memastikan semua peranti menerima data konfigurasi yang disegerakkan.

Spesifikasi XCV200-6FG456C

|

Jenis |

Parameter |

|

Pengilang |

AMD XILINX

|

|

Siri |

Virtex® |

|

Pembungkusan |

Dulang |

|

Status bahagian |

Usang |

|

Bilangan makmal/clbs |

1176 |

|

Bilangan elemen/sel logik |

5292 |

|

Jumlah bit RAM |

57344 |

|

Bilangan I/O. |

284 |

|

Bilangan pintu |

236666 |

|

Voltan - bekalan |

2.375V ~ 2.625V |

|

Jenis pemasangan |

Permukaan gunung |

|

Suhu operasi |

0 ° C ~ 85 ° C (TJ) |

|

Pakej / kes |

456-BBGA |

|

Pakej peranti pembekal |

456-FBGA (23x23) |

|

Nombor produk asas |

XCV200 |

Aplikasi XCV200-6FG456C

Telekomunikasi dan rangkaian

XCV200-6FG456C cemerlang dalam aplikasi telekomunikasi dan rangkaian kerana keupayaannya untuk mengendalikan transmisi data berkelajuan tinggi dan tugas pemprosesan isyarat kompleks.Kiraan gerbang yang tinggi dan keupayaan I/O yang teguh membolehkan ia menyokong fungsi seperti pemprosesan paket, modulasi isyarat/demodulasi, dan protokol pembetulan ralat.

Pemprosesan Isyarat Digital (DSP)

Sesuai untuk aplikasi DSP, FPGA ini boleh melakukan perhitungan matematik yang cepat dan kompleks yang diperlukan dalam teknologi pemprosesan audio dan video.Sama ada untuk sistem multimedia, pengiktirafan suara, atau perkhidmatan streaming, keupayaan pemprosesan kuat XCV200-6FG456C dan pemprosesan isyarat memori tertanam yang cekap dan pemprosesan isyarat berkualiti tinggi.

Sistem Kawalan Perindustrian

Dalam automasi perindustrian, XCV200-6FG456C menyediakan prestasi yang diperlukan untuk menguruskan sistem kawalan dan rangkaian automasi.Keupayaannya untuk melaksanakan pelbagai tugas kawalan secara serentak sambil memastikan masa tindak balas menjadikannya sesuai untuk aplikasi dalam kawalan proses, robotik, dan penglihatan mesin.

Instrumen perubatan

Ketepatan dan kelajuan FPGA adalah hebat dalam pengimejan perubatan dan peralatan diagnostik, di mana ia membantu dalam pemprosesan algoritma kompleks untuk aplikasi pengimejan seperti MRI, ultrasound, dan imbasan CT.Keupayaan XCV200-6FG456C memastikan bahawa ia dapat mengendalikan pemprosesan data yang tinggi dan pemprosesan rumit yang diperlukan dalam teknologi perubatan moden.

XCV200-6FG456C Bahagian yang sama

Langkah pengaturcaraan XCV200-6FG456C

Langkah pengaturcaraan untuk XCV200-6FG456C:

1. Kemasukan reka bentuk

Fasa awal pengaturcaraan FPGA melibatkan menentukan logik dan fungsi digital sistem anda.Ini boleh dilakukan dengan menggunakan bahasa penerangan perkakasan (HDLS) seperti VHDL atau Verilog, di mana anda menulis kod yang menentukan bagaimana FPGA memproses data dan berinteraksi dengan perkakasan lain.Alat kemasukan skematik yang terdapat dalam perisian reka bentuk FPGA seperti Xilinx ISE atau Vivado boleh digunakan.Kaedah ini melibatkan mewujudkan perwakilan visual logik dengan menyeret dan menjatuhkan komponen, yang mana beberapa mendapati lebih intuitif daripada kod menulis.

2. Sintesis

Sebaik sahaja reka bentuk selesai, langkah seterusnya adalah sintesis, di mana alat seperti Xilinx's XST (Teknologi Sintesis Xilinx) mengubah kod HDL atau reka bentuk skema anda ke dalam senarai netl.Netlist ini menerangkan litar dari segi komponen digital generik, seperti pintu logik dan daftar.Proses sintesis juga melibatkan mengoptimumkan reka bentuk untuk memenuhi keperluan prestasi dan meminimumkan penggunaan sumber untuk operasi FPGA yang cekap.

3. Pelaksanaan

Proses pelaksanaan bermula dengan terjemahan, menggabungkan reka bentuk anda dengan fail kekangan yang menentukan parameter seperti frekuensi jam dan tugasan pin.Berikutan terjemahan, peringkat pemetaan memberikan unsur-unsur netlist anda kepada sumber fizikal tertentu pada FPGA, seperti jadual paparan (LUTs) dan flip-flop.Fasa penempatan dan penghalaan kemudian menentukan lokasi fizikal setiap komponen dalam seni bina FPGA dan mewujudkan hubungan di antara mereka melalui sumber interkoneksi yang boleh diprogramkan.Tahap ini sangat bagus untuk mencapai metrik prestasi yang dikehendaki, termasuk frekuensi jam.

4. Generasi Bitstream

Selepas penempatan dan penghalaan yang berjaya, alat ini menghasilkan bitstream, fail konfigurasi binari yang mengandungi semua maklumat pengaturcaraan untuk FPGA.Ia sering disyorkan untuk mensimulasikan reka bentuk akhir penempatan akhir untuk memastikan bitstream akan berkelakuan seperti yang dijangkakan di bawah syarat-syarat.Langkah pengesahan ini membantu mengelakkan isu -isu yang berpotensi semasa operasi sebenar.

5. Konfigurasi

Langkah terakhir melibatkan memuatkan bitstream ke dalam FPGA menggunakan pelbagai kaedah konfigurasi.Mod siri hamba, pilihan yang mudah dan kos efektif, mengkonfigurasi FPGA melalui peranti induk luaran yang menghantar data secara bersiri.Dalam mod Serial Master, FPGA secara autonomi membaca bitstream dari prom bersiri yang dilampirkan.Untuk konfigurasi berkelajuan tinggi, mod SelectMap membolehkan mikropemproses luaran untuk memuatkan data ke FPGA dengan cepat.Di samping itu, mod JTAG digunakan bukan sahaja untuk pengaturcaraan tetapi juga untuk menguji dan menyahpepijat, menggunakan antara muka standard untuk pengaturcaraan dalam sistem dan ujian imbasan sempadan.

XCV200-6FG456C Kelebihan

Prestasi

Siri Xilinx Virtex, yang mana XCV200-6FG456C dimiliki, dioptimumkan untuk prestasi berkelajuan tinggi, menawarkan kadar jam sistem sehingga 200 MHz.Ini menjadikannya sesuai untuk aplikasi yang memerlukan pemprosesan data yang cepat, memastikan pengendalian algoritma kompleks dan operasi berkelajuan tinggi seperti telekomunikasi, pemprosesan, dan multimedia.

Sokongan piawaian I/O.

FPGA ini menyokong pelbagai standard input/output, termasuk LVTTL, LVCMOS, PCI, GTL, HSTL, SSTL, CTT, dan AGP.Sokongan piawaian I/O yang luas membolehkan XCV200-6FG456C untuk mengintegrasikan dengan lancar dengan pelbagai komponen sistem, meningkatkan utilitinya merentasi ekosistem digital yang pelbagai.Fleksibiliti ini membolehkan untuk menyesuaikan FPGA ke keadaan interfacing yang berbeza tanpa pengubahsuaian sistem.

Pengurusan Jam

XCV200-6FG456C menggabungkan pelbagai gelung terkunci kelewatan (DLL) untuk pengedaran dan pengurusan jam dalam sistem.DLL ini membantu meningkatkan masa dan kebolehpercayaan sistem dengan menyediakan isyarat jam yang tepat yang diperlukan untuk operasi segerak.Ciri ini penting dalam mengurangkan kesilapan sistem dan meningkatkan prestasi keseluruhan, terutamanya dalam reka bentuk kompleks yang memerlukan masa dan penyegerakan yang tepat.

Fleksibiliti reka bentuk

Dengan 1,176 blok logik yang boleh dikonfigurasikan dan 5,292 sel logik, XCV200-6FG456C menawarkan sumber logik yang besar dengan keupayaan untuk melaksanakan pelbagai fungsi.Dari logik gam mudah ke sistem digital yang rumit, FPGA ini menyokong keperluan reka bentuk yang kompleks, menjadikannya sesuai untuk aplikasi dalam pengkomputeran tersuai, pemprosesan isyarat digital, dan prototaip.

Prototaip cepat

FPGA seperti XCV200-6FG456C terkenal dengan keupayaan mereka untuk menyokong prototaip pesat.Peranti ini membolehkan lelaran reka bentuk cepat dan boleh dikonfigurasikan semula dalam bidang, yang merupakan kelebihan untuk kitaran pembangunan kerana ia mengurangkan masa ke pasaran.Ia juga menyesuaikan diri dengan cekap untuk mengubah keperluan atau kemas kini dalam spesifikasi projek, memastikan produk akhir terkini dengan piawaian teknologi terkini.

Keupayaan integrasi

Keupayaan integrasi XCV200-6FG456C memudahkan penyatuan pelbagai komponen diskret ke dalam cip tunggal.Integrasi ini boleh menyebabkan kerumitan sistem yang dikurangkan, penggunaan kuasa yang lebih rendah, dan penjimatan kos.Dengan meminimumkan bilangan komponen berasingan yang diperlukan, FPGA ini memudahkan proses reka bentuk dan meningkatkan kebolehpercayaan dan kekompakan sistem keseluruhan.

Dimensi pembungkusan XCV200-6FG456C

XCV200-6FG456C adalah Array Gate Programmable Field (FPGA) dari Siri Virtex® AMD, yang ditempatkan dalam pakej Grid Fine-Pitch Grid (FBGA) 456-ball.

• Jenis Pakej: 456-FBGA

• Saiz pakej: 23 mm x 23 mm

• Padang bola: 1.0 mm

XCV200-6FG456C Pengilang

XCV200-6FG456C adalah Array Gate Programmable Field (FPGA) yang asalnya dibangunkan oleh Xilinx, sebuah syarikat yang terkenal dengan peranti logik yang boleh diprogramkan berprestasi tinggi.Mengikuti pengambilalihan Xilinx oleh Amd, XCV200-6FG456C kini dikaitkan dengan AMD sebagai pengeluar semasa.Walau bagaimanapun, model FPGA ini usang dan tidak lagi dalam pengeluaran.AMD terus menyokong seni bina FPGA yang lebih baru dengan prestasi yang dipertingkatkan, kecekapan kuasa, dan panjang umur yang diperluaskan, menjadikan alternatif moden lebih baik untuk reka bentuk baru.

Kesimpulan

XCV200-6FG456C adalah FPGA yang serba boleh dan berkelajuan tinggi, berguna untuk banyak aplikasi teknologi.Walaupun ia tidak lagi dibuat, ia masih merupakan pilihan yang baik untuk sistem yang lebih lama yang memerlukan prestasi yang boleh dipercayai.Panduan ini telah merangkumi reka bentuk, langkah pengaturcaraan, dan kegunaan praktikal, menjadikannya lebih mudah untuk memahami bagaimana ia berfungsi dan bagaimana ia boleh digunakan.Memandangkan FPGA yang lebih baru tersedia, anda boleh menggunakan pengetahuan ini untuk memilih FPGA yang sesuai untuk keperluan anda dan meningkatkan reka bentuk digital.

Datasheet pdf

XCV200-6FG456C datasheets:

Tentang kita

ALLELCO LIMITED

Baca lebih lanjut

Siasatan Pantas.

Sila hantar pertanyaan, kami akan bertindak balas dengan segera.

Soalan yang sering ditanya [FAQ]

1. Apakah penggunaan kuasa XCV200-6FG456C?

XCV200-6FG456C beroperasi pada 2.5V, dengan julat voltan 2.375V hingga 2.625V.Penggunaan kuasa bergantung kepada penggunaan logik dan kekerapan jam, tetapi sebagai FPGA yang lebih tua, ia mungkin kurang cekap kuasa daripada peranti Xilinx yang lebih baru.Pengurusan kuasa yang betul dan pelesapan haba harus dipertimbangkan.

2. Bagaimana XCV200-6FG456C berbanding dengan XCV200-6FG256C?

XCV200-6FG456C mempunyai pakej yang lebih besar (456-ball FBGA) berbanding dengan XCV200-6FG256C (256-ball FBGA), yang menawarkan lebih banyak pin I/O (284 vs 172) dan berpotensi lebih baik untuk aplikasi yang memerlukan interfacing yang luas.Jika reka bentuk anda bergantung pada lebih banyak keupayaan I/O, XCV200-6FG456C adalah pilihan yang lebih baik.

3. Bolehkah saya memprogram semula XCV200-6FG456C beberapa kali?

Ya, XCV200-6FG456C adalah FPGA berasaskan SRAM, yang bermaksud ia dapat diprogramkan semula bilangan kali tanpa had selagi kuasa dibekalkan.Walau bagaimanapun, anda memerlukan memori yang tidak menentu luaran (EEPROM atau FLASH) untuk mengekalkan bitstream selepas kitaran kuasa.

4. Adakah XCV200-6FG456C menyokong komunikasi bersiri berkelajuan tinggi?

XCV200-6FG456C menyokong pelbagai piawaian I/O seperti LVTTL, LVCMOS, PCI, GTL, HSTL, dan SSTL, tetapi ia tidak mempunyai SERDES berkelajuan tinggi (serializer/deserializer) atau transceiver seperti FPGAS moden.Bagi aplikasi yang memerlukan pautan siri berkelajuan tinggi (mis., PCIe, Gigabit Ethernet, atau HDMI), pertimbangkan model FPGA yang lebih baru.

5. Bagaimanakah XCV200-6FG456C berbanding dengan model FPGA yang lebih baru?

XCV200-6FG456C tergolong dalam generasi FPGA yang lebih tua.Berbanding dengan FPGA Virtex moden, ia mempunyai kiraan pintu yang lebih rendah, kelajuan jam yang lebih perlahan, dan kecekapan kuasa terhad.Model yang lebih baru menawarkan ketumpatan logik yang lebih tinggi, memori yang lebih tertanam, blok DSP maju, dan penggunaan kuasa yang lebih rendah, menjadikannya lebih baik untuk aplikasi moden.

AD733322AR Pinout, Ciri, dan Butiran Teknikal Diterangkan

pada 2025/03/21

EP20K100EFC324-1X FPGA: Ciri, Spesifikasi, Aplikasi, dan Panduan Pengaturcaraan

pada 2025/03/20

Jawatan popular

-

Arahan Kompleks Set Komputer: Bagaimana mereka menukar pengkomputeran?

pada 8000/04/19 147782

-

USB-C Pinout dan Ciri

pada 2000/04/19 112072

-

Menggunakan Primitif Simulasi Unified Xilinx: Panduan Komprehensif untuk Reka Bentuk dan Simulasi FPGA

pada 1600/04/19 111352

-

Voltan Bekalan Kuasa dalam Elektronik: Maksud VCC, VDD, VEE, VSS dan GND

pada 0400/04/19 83829

-

Panduan Penyambung RJ45: PINOUT, Pendawaian, Jenis Kabel, dan Kegunaan

pada 1970/01/1 79643

-

Panduan Terbaik untuk Kod Warna Kawat dalam Sistem Elektrik Moden

Cara sistem elektrik kita menggunakan warna bukan hanya untuk kelihatan.Setiap warna wayar kini menunjukkan fungsi tertentu, menjadikannya lebih mudah untuk mengenal pasti dan mengendalikan kompone...pada 1970/01/1 67006

-

Panduan Injap Purge: Fungsi, Gejala, Ujian, dan Penggantian Prestasi Enjin Optimal

Injap pembersihan adalah bahagian utama sistem kereta yang membantu menjaga udara bersih dengan menguruskan wap bahan api sebelum mereka dapat melarikan diri ke atmosfera.Ini bukan sahaja membantu ...pada 1970/01/1 63134

-

Faktor Kualiti (Q): Persamaan dan Aplikasi

Faktor kualiti, atau 'Q', adalah penting apabila memeriksa bagaimana induktor dan resonator berfungsi dalam sistem elektronik yang menggunakan frekuensi radio (RF).'Q' mengukur seberapa baik litar ...pada 1970/01/1 63067

-

Mencapai prestasi puncak dengan teorem pemindahan kuasa maksimum

Teorem pemindahan kuasa maksimum menerangkan bagaimana tenaga dari sumber, seperti bateri atau penjana, mengalir ke beban yang disambungkan.Ia menunjukkan keadaan yang tepat di mana beban menerima ...pada 1970/01/1 54098

-

Spesifikasi dan keserasian bateri A23

Bateri A23 adalah bateri berbentuk silinder kecil dengan voltan tinggi.Juga dipanggil 23A, 23AE, atau MN21, ia berjalan pada 12 volt dan lebih tinggi daripada bateri AA atau AAA.Reka bentu...pada 1970/01/1 52226