EPM7192SQC160-15 CPLD: Ciri, PINOUT, Pengaturcaraan dan Aplikasi

Panduan ini bercakap mengenai EPM7192SQC160-15, cip logik yang boleh diprogramkan dari keluarga Max 7000s.Ia menerangkan apa yang boleh dilakukan cip, bagaimana ia berfungsi, dan di mana ia boleh digunakan.Ia menunjukkan bagaimana cip dibina di dalam, apa yang setiap pin lakukan, dan bagaimana ia menghubungkan ke bahagian lain.Panduan ini juga termasuk di mana cip ini boleh digunakan, bagaimana untuk memprogramnya langkah demi langkah, apa cip yang serupa ada, dan siapa yang membuatnya.Katalog

Apakah EPM7192SQC160-15?

The EPM7192SQC160-15 adalah CPLD mid-range (peranti logik yang boleh diprogramkan kompleks) dari keluarga Max 7000s, yang dibuat untuk kawalan logik digital yang boleh dipercayai dalam sistem tertanam dan perindustrian.Cip ini menawarkan 192 macrocells dan kira -kira 3,750 pintu logik, menyediakan kapasiti yang mencukupi untuk mengendalikan tugas logik sederhana.Ia termasuk 124 pin I/O, dan berjalan pada bekalan 5V, dengan sokongan multivolt I/O untuk antara muka dengan kedua -dua sistem logik 3.3V dan 5V.Senibina berasaskan EEPROM yang boleh diprogramkan dalam sistem ini bermakna anda boleh memprogramnya secara langsung di litar anda menggunakan JTAG, tanpa memerlukan komponen tambahan atau memori luaran.Dengan gred kelajuan -15, ia menyokong frekuensi jam sistem sehingga kira-kira 76.9 MHz, menawarkan prestasi masa yang cepat dan konsisten untuk aplikasi digital yang luas.Keluarga Max 7000s terkenal dengan prestasi pepejal, memori EEPROM, dan operasi voltan fleksibel.

Mencari EPM7192SQC160-15?Hubungi kami untuk menyemak stok semasa, masa utama, dan harga.

EPM7192SQC160-15 Model CAD

EPM7192SQC160-15 Simbol

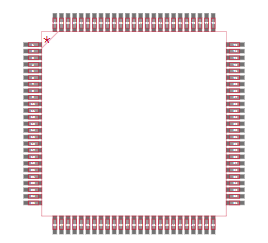

EPM7192SQC160-15 Jejak

EPM7192SQC160-15 Model 3D

Ciri-ciri EPM7192SQC160-15

192 MacRocells: Peranti ini merangkumi 192 macrocells, yang berfungsi sebagai elemen yang boleh diprogramkan teras.Macrocells ini boleh dikonfigurasikan untuk melaksanakan pelbagai fungsi logik gabungan dan berurutan yang diperlukan dalam reka bentuk digital.

Kira -kira 3,750 pintu logik: Ia menawarkan kapasiti logik yang setara sekitar 3,750 pintu, menjadikannya sesuai untuk logik kawalan kerumitan sederhana, mesin negara, atau logik gam dalam sistem tertanam.

Pengaturcaraan dalam sistem melalui JTAG: Ia mempunyai memori berasaskan EEPROM yang membolehkan pemrograman semula secara langsung dalam sistem menggunakan antara muka JTAG standard, menyokong kedua-dua piawaian IEEE 1149.1 dan IEEE 1532.

Kekerapan maksimum hingga 125 mHz: Logik dalaman boleh beroperasi pada kelajuan jam mencapai 125 MHz, membolehkan pemprosesan cepat untuk aplikasi sensitif masa.

Kelewatan penyebaran 7.5 ns: Cip menawarkan kelewatan penyebaran yang rendah kira -kira 7.5 nanodekonda, memastikan tindak balas isyarat pesat dari input ke output.

Menyokong bekalan 5V dengan multivolt I/O: Peranti berjalan pada bekalan teras 5V dan menyokong multivolt I/O, yang membolehkan keserasian dengan tahap isyarat 5V dan 3.3V untuk integrasi mudah ke dalam sistem voltan campuran.

Kadar membunuh dan output terbuka yang boleh diprogramkan: Anda boleh mengawal kadar kelebihan isyarat untuk pengurangan EMI dan pilih output terbuka untuk peralihan dan logik atau peralihan tahap.

Enam output global membolehkan isyarat: Isyarat kawalan global ini membolehkan membolehkan atau melumpuhkan output merentasi pelbagai bank I/O untuk pengurusan isyarat yang cekap.

Flip-flop yang boleh dikonfigurasikan dalam macrocells: Setiap MacRocell termasuk flip-flop yang menyokong pratetap, jelas, jam membolehkan, dan kawalan individu, menyediakan fleksibiliti yang dipertingkatkan untuk reka bentuk logik berurutan.

Mod kuasa rendah: Peranti ini termasuk ciri penjimatan kuasa yang boleh mengurangkan penggunaan kuasa macrocell sebanyak lebih daripada 50%, yang bermanfaat untuk aplikasi yang cekap tenaga.

Sokongan ujian imbasan sempadan JTAG : Peranti dengan 128 atau lebih macrocells, seperti ini, termasuk ciri ujian sempadan penuh untuk diagnostik dan pengesahan peringkat papan yang cekap.

Bit keselamatan untuk perlindungan reka bentuk: Bit keselamatan yang boleh diprogramkan memastikan bahawa reka bentuk dalaman tidak dapat dibaca atau disalin, melindungi harta intelek.

I/O serasi PCI: Struktur I/O direka untuk memenuhi keperluan elektrik PCI, membolehkan interfacing langsung dengan sistem berasaskan PCI.

Julat suhu operasi 0 ° C hingga 70 ° C: Julat suhu gred komersil standard menjadikan peranti ini sesuai untuk kebanyakan aplikasi persekitaran dalaman dan terkawal.

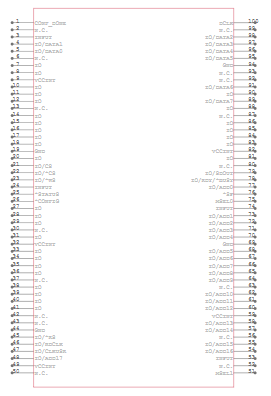

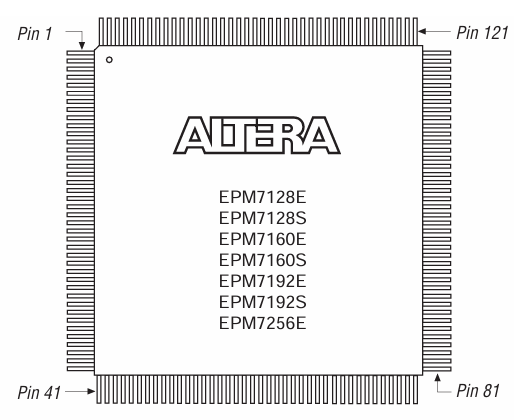

EPM7192SQC160-15 Diagram Pinout

Rajah ini menunjukkan susun atur pin untuk peranti EPM7192SQC160-15 dan peranti Altera Max yang serupa.Cip itu mempunyai 160 pin yang disusun di sekitar empat sisi dalam pakej QFP persegi.Pin 1 bermula di sudut kiri atas dan nombor pergi berlawanan arah jam di sekitar cip.Setiap sisi mempunyai 40 pin.Titik kecil di bahagian atas kiri pin 1, yang membantu dengan penempatan yang betul.Nama cip di pusat menunjukkan ia serasi dengan model lain dalam keluarga yang sama.Susun atur ini menyediakan banyak sambungan I/O dan berguna untuk reka bentuk logik yang kompleks.

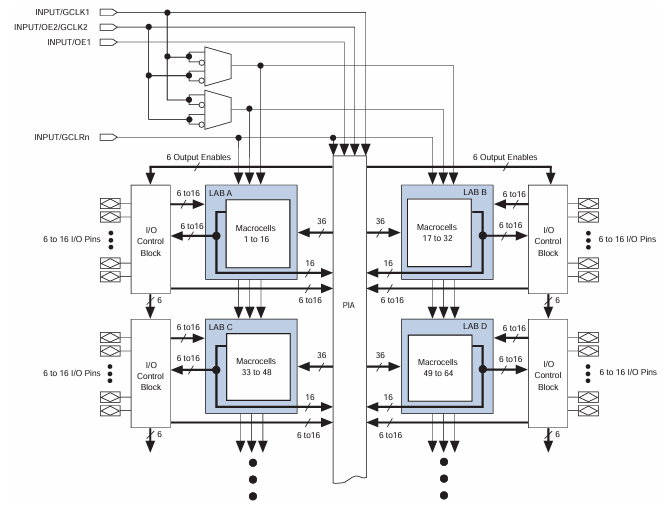

Rajah Blok Max 7000s

Rajah blok ini menunjukkan struktur dalaman Max 7000s CPLD, termasuk EPM7192SQC160-15.Cip dibahagikan kepada empat bahagian utama yang dipanggil blok array logik (makmal A hingga D).Setiap makmal mempunyai 16 makro, yang merupakan unit logik kecil yang digunakan untuk membina litar digital.Bersama -sama, makmal ini mengendalikan operasi logik kompleks.

Di tengah -tengah adalah Array Interconnect Programmable (PIA), yang menghubungkan semua makmal dan membolehkan mereka berkongsi data.Setiap makmal menghantar dan menerima isyarat melalui 36 saluran, memberikan penghalaan fleksibel antara blok logik.Sekitar tepi, terdapat blok kawalan I/O yang menghubungkan 6 hingga 16 pin I/O ke setiap makmal, yang membolehkan peranti menyambung dengan bahagian lain sistem.

Di bahagian atas, isyarat kawalan global seperti jam dan output membolehkan ditunjukkan.Isyarat ini membantu menguruskan bagaimana data bergerak di dalam cip dan apabila output aktif.Secara keseluruhannya, rajah menunjukkan bagaimana EPM7192SQC160-15 menganjurkan logik dan sambungannya untuk menyokong reka bentuk digital tersuai.

Spesifikasi EPM7192SQC160-15

|

Jenis |

Parameter |

|

Pengilang |

Altera |

|

Siri |

Max® 7000s |

|

Pembungkusan |

Dulang |

|

Status bahagian |

Usang |

|

Jenis yang boleh diprogramkan |

Dalam sistem yang boleh diprogramkan |

|

Kelewatan masa tpd (1) maksimum |

15 ns |

|

Bekalan Voltan - Dalaman |

4.75V ~ 5.25V |

|

Bilangan elemen logik/blok |

12 |

|

Bilangan macrocells |

192 |

|

Bilangan pintu |

3750 |

|

Bilangan I/O. |

124 |

|

Suhu operasi |

0 ° C ~ 70 ° C (TA) |

|

Jenis pemasangan |

Permukaan gunung |

|

Pakej / kes |

160-BQFP |

|

Pakej peranti pembekal |

160-PQFP (28x28) |

|

Nombor produk asas |

EPM7192 |

Aplikasi EPM7192SQC160-15

Logik gam sistem tertanam

EPM7192SQC160-15 sangat sesuai untuk merapatkan peranti digital yang berbeza dalam sistem tertanam.Ia boleh digunakan untuk menguruskan komunikasi antara mikrokontroler, cip memori, dan peranti I/O dengan mengendalikan pengekodan alamat, kawalan bas, dan pelarasan masa tanpa memerlukan ICS logik diskret.

Mesin negeri dan logik kawalan

Dengan 192 MacRocells, cip itu sesuai untuk melaksanakan mesin negara tersuai dan logik kawalan.Ia biasanya digunakan dalam tugas automasi, pengawal motor, dan sistem kawalan berasaskan masa yang memerlukan peralihan keadaan yang boleh dipercayai dan berulang.

Antara muka protokol komunikasi

CPLD ini boleh diprogramkan untuk membuat atau menterjemahkan protokol komunikasi seperti UART, SPI, I²C, atau format siri adat.Ia membolehkan konfigurasi dan pengubahsuaian mudah tanpa mengubah perkakasan, menjadikannya berharga untuk interfacing komunikasi.

Pra-pemprosesan isyarat digital

Terima kasih kepada kelajuan logik yang cepat dan kelewatan penyebaran yang rendah, ia boleh mengendalikan tugas pemprosesan isyarat mudah seperti penapisan, multiplexing, atau pengesanan tepi sebelum isyarat mencapai pemproses utama atau cip DSP.

Terjemahan antara muka dan peralihan tahap

Keupayaan multivolt I/Onya menyokong kedua -dua isyarat 3.3V dan 5V.Ini menjadikannya sesuai untuk reka bentuk yang termasuk komponen yang beroperasi pada tahap voltan yang berbeza, yang membolehkan terjemahan voltan yang selamat dan cekap.

Prototaip cepat dan kemas kini sistem

Anda boleh menggunakan cip ini dalam sistem yang mungkin memerlukan kemas kini logik yang kerap.Struktur berasaskan EEPROM dan antara muka pengaturcaraan JTAG memungkinkan untuk memprogram semula logik walaupun selepas papan dipasang.

Ujian dan Diagnostik Tahap Lembaga

Dengan sokongan imbasan sempadan melalui JTAG, ia menguji sambungan antara cip pada PCB tanpa memerlukan probe.Ini berguna semasa diagnostik pembuatan dan di lapangan untuk mengesan isu pematerian atau penghalaan.

EPM7192SQC160-15 Bahagian yang sama

• EPM7192EQC160-20 (Alta)

Peranti ini adalah dari siri Max 7000 yang sama dan menawarkan sumber logik yang sama, 192 MacRocells dan 124 I/O pin dalam pakej PQFP 160-pin.Ia beroperasi pada gred kelajuan yang lebih perlahan -20, bermakna ia mempunyai kelewatan penyebaran yang lebih lama (~ 20 ns), tetapi ia masih memenuhi keperluan reka bentuk bukan kritikal.Ia adalah alternatif yang sesuai untuk aplikasi di mana ketumpatan logik adalah penting, tetapi masa ultra cepat tidak menjadi keutamaan, menjadikannya sesuai untuk projek-projek sensitif kos yang masih memerlukan kesetaraan fungsional.

• EPM7192SQI160-10N (Alta)

Bahagian ini juga bersesuaian logik dengan EPM7192SQC160-15, yang menawarkan jumlah macrocells dan I/OS yang sama.Walau bagaimanapun, ia menggunakan gred kelajuan -10, yang menyokong operasi lebih cepat dengan masa yang lebih baik (kelewatan penyebaran 10 ns).Ia juga menyokong julat suhu lanjutan dari -40 ° C hingga +85 ° C, menjadikannya pengganti yang sangat baik untuk aplikasi perindustrian atau luaran.Ini menjadikannya ideal apabila kelajuan yang lebih tinggi dan ketahanan alam sekitar diperlukan.

• EPM7192SQC160-7 (Intel)

Sebagai varian laju langsung EPM7192SQC160-15, versi -7 menyampaikan prestasi terpantas dalam keluarga, dengan penyebaran kelewatan hingga 7.5 ns.Ia mengekalkan konfigurasi pin yang sama, spesifikasi kuasa, dan ketumpatan logik, yang menawarkan penggantian drop-in bagi mereka yang mencari kelajuan yang lebih baik tanpa mengubah susun atur papan atau keperluan voltan.Ini menjadikannya pilihan terbaik untuk reka bentuk masa kritikal yang memerlukan tindak balas isyarat yang lebih cepat sambil tinggal di dalam jejak reka bentuk yang sama.

Langkah-langkah pengaturcaraan EPM7192SQC160-15

1. Masukkan mod ISP

Langkah pertama adalah untuk mengalihkan peranti ke mod ISP (pengaturcaraan dalam sistem).Ini dilakukan melalui antara muka JTAG.Sekali dalam mod ISP, semua pin I/O pada peranti dimasukkan ke dalam mod Tri-State yang selamat untuk mengelakkan gangguan logik yang tidak diingini semasa pengaturcaraan.Inisialisasi ini biasanya mengambil kira -kira 1 milisaat.

2. Semak ID peranti

ID silikon yang unik tertanam dalam peranti untuk mengesahkan model yang betul sebelum pengaturcaraan bermula.Sistem beralih dalam arahan baca dan mengambil ID melalui baris TDO (Data Ujian).Pemeriksaan ini memastikan bahawa alat pengaturcaraan disambungkan ke CPLD yang betul dan mengelakkan kesilapan seperti menimpa bahagian yang berbeza.

3. memadam pukal

Pemadaman pukal membersihkan semua data yang disimpan sebelum ini dalam ingatan EEPROM CPLD.Ini menyediakan cip untuk menerima konfigurasi baru.Perintah pemadam memulakan nadi yang biasanya berlangsung sekitar 100 milisaat, memastikan semua sel yang boleh diprogramkan diset semula.

4. Program EEPROM

Data konfigurasi baru dimuatkan ke dalam peranti dengan mengalihkan alamat dan bit data melalui port JTAG.Setiap sel memori ditulis satu persatu, dengan nadi pengaturcaraan yang digunakan selepas setiap kitaran menulis yang berjaya.Proses ini mentakrifkan struktur logik yang akan digunakan oleh CPLD apabila dikuasakan.

5. Sahkan EEPROM

Selepas pengaturcaraan, peranti melakukan langkah pengesahan.Ini melibatkan membaca semula setiap lokasi memori yang diprogramkan dan membandingkan nilai output terhadap data yang dimaksudkan.Jika pengesahan gagal, proses mesti diulang.Langkah ini menjamin konfigurasi telah berjaya ditulis.

6. Keluar mod ISP

Sebaik sahaja pengesahan selesai, arahan akhir dikeluarkan untuk keluar dari mod ISP.Peranti mengaktifkan semula pin I/Onya dan menyambung semula operasi normal.Peralihan ini juga mengambil masa kira-kira 1 milisaat dan melengkapkan kitaran pengaturcaraan dalam sistem.

EPM7192SQC160-15 Dimensi pembungkusan

• Saiz badan: 28mm × 28mm

• Ketinggian pakej: 3.4mm

• Padang pin: 0.65mm

EPM7192SQC160-15 Pengilang

EPM7192SQC160-15 pada asalnya dihasilkan oleh Altera Corporation, sebuah syarikat yang terkenal dengan peranti logik yang boleh diprogramkan.Pada tahun 2015, Altera diperolehi oleh Intel Corporation, dan peranti ini kini menjadi sebahagian daripada kumpulan penyelesaian yang boleh diprogramkan Intel di bawah keluarga CPLD MAX 7000S.Intel terus menyokong produk Altera Legacy, walaupun EPM7192SQC160-15 kini diklasifikasikan sebagai usang dalam kebanyakan katalog rasmi.Walaupun statusnya yang dihentikan, reputasi sejarah Intel untuk kebolehpercayaan dan warisan Altera dalam penyelesaian logik berprestasi tinggi memastikan permintaan dan ketersediaan berterusan melalui pengedar sekunder.

Kesimpulan

EPM7192SQC160-15 adalah cip yang berguna dan fleksibel untuk mengendalikan tugas kawalan digital dalam banyak sistem elektronik.Ia menawarkan kuasa logik yang cukup untuk pekerjaan seperti membina mesin negara tersuai, isyarat pengendalian, dan menghubungkan peranti yang berbeza.Ia menyokong tahap voltan yang berbeza, berfungsi pada kelajuan cepat, dan boleh dikemas kini dengan mudah melalui JTAG.Reka bentuk dalamannya membolehkan aliran isyarat lancar dan perubahan logik yang mudah.Walaupun ia kini dihentikan, ia masih merupakan pilihan yang baik untuk projek lama atau berterusan, dan boleh digantikan dengan cip yang sama yang menawarkan sokongan suhu yang lebih cepat atau lebih luas.

Datasheet pdf

EPM7192SQC160-15 Datasheets:

Tentang kita

ALLELCO LIMITED

Baca lebih lanjut

Siasatan Pantas.

Sila hantar pertanyaan, kami akan bertindak balas dengan segera.

Soalan yang sering ditanya [FAQ]

1. Bolehkah saya memprogram EPM7192SQC160-15 tanpa mengeluarkannya dari papan litar?

Ya, cip itu menyokong pengaturcaraan di sistem (ISP) melalui antara muka JTAG, jadi anda boleh memprogram atau memprogramnya secara langsung semasa ia disolder pada PCB, yang memudahkan kemas kini reka bentuk dan mengurangkan kerja semula.

2. Apa perisian pengaturcaraan yang harus saya gunakan untuk EPM7192SQC160-15?

Anda boleh menggunakan perisian Altera Quartus II (versi lama) untuk membuat reka bentuk logik, menyusun kod, dan menguruskan proses pengaturcaraan berasaskan JTAG.Quartus II menyokong peranti Max 7000s seperti EPM7192SQC160-15.

3. Adakah EPM7192SQC160-15 memerlukan memori luaran untuk operasi?

Tidak, ia mempunyai memori konfigurasi berasaskan EEPROM dalaman.Semua konfigurasi logik disimpan di dalam cip, jadi tiada memori luaran diperlukan untuk menyimpan keadaan logik atau urutan boot.

4. Apa yang menjadikan EPM7192SQC160-15 sesuai untuk kegunaan perindustrian?

Operasi 5V yang teguh, keserasian multivolt I/O, pemprosesan logik cepat, dan memori yang tidak menentu berasaskan EEPROM menjadikannya boleh dipercayai untuk sistem perindustrian yang memerlukan fungsi logik digital yang stabil dan tahan lama.

5. Bagaimana EPM7192SQC160-15 Mengendalikan Sistem Voltan Campuran?

Terima kasih kepada sokongan Multivolt I/O, peranti boleh berinteraksi dengan kedua-dua tahap logik 3.3V dan 5V, menjadikannya sesuai untuk sistem isyarat campuran dan interfacing dengan komponen voltan rendah moden.

Mengapa Pilih EPF10K100EFC484-3 untuk projek anda

pada 2025/06/13

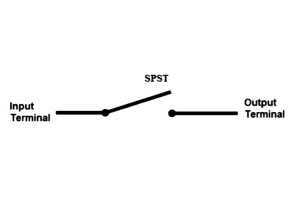

Apakah suis SPST dan bagaimana ia berfungsi?

pada 2025/06/12

Jawatan popular

-

Arahan Kompleks Set Komputer: Bagaimana mereka menukar pengkomputeran?

pada 8000/04/18 147780

-

USB-C Pinout dan Ciri

pada 2000/04/18 112050

-

Menggunakan Primitif Simulasi Unified Xilinx: Panduan Komprehensif untuk Reka Bentuk dan Simulasi FPGA

pada 1600/04/18 111352

-

Voltan Bekalan Kuasa dalam Elektronik: Maksud VCC, VDD, VEE, VSS dan GND

pada 0400/04/18 83806

-

Panduan Penyambung RJ45: PINOUT, Pendawaian, Jenis Kabel, dan Kegunaan

pada 1970/01/1 79608

-

Panduan Terbaik untuk Kod Warna Kawat dalam Sistem Elektrik Moden

Cara sistem elektrik kita menggunakan warna bukan hanya untuk kelihatan.Setiap warna wayar kini menunjukkan fungsi tertentu, menjadikannya lebih mudah untuk mengenal pasti dan mengendalikan kompone...pada 1970/01/1 66988

-

Panduan Injap Purge: Fungsi, Gejala, Ujian, dan Penggantian Prestasi Enjin Optimal

Injap pembersihan adalah bahagian utama sistem kereta yang membantu menjaga udara bersih dengan menguruskan wap bahan api sebelum mereka dapat melarikan diri ke atmosfera.Ini bukan sahaja membantu ...pada 1970/01/1 63113

-

Faktor Kualiti (Q): Persamaan dan Aplikasi

Faktor kualiti, atau 'Q', adalah penting apabila memeriksa bagaimana induktor dan resonator berfungsi dalam sistem elektronik yang menggunakan frekuensi radio (RF).'Q' mengukur seberapa baik litar ...pada 1970/01/1 63049

-

Mencapai prestasi puncak dengan teorem pemindahan kuasa maksimum

Teorem pemindahan kuasa maksimum menerangkan bagaimana tenaga dari sumber, seperti bateri atau penjana, mengalir ke beban yang disambungkan.Ia menunjukkan keadaan yang tepat di mana beban menerima ...pada 1970/01/1 54097

-

Spesifikasi dan keserasian bateri A23

Bateri A23 adalah bateri berbentuk silinder kecil dengan voltan tinggi.Juga dipanggil 23A, 23AE, atau MN21, ia berjalan pada 12 volt dan lebih tinggi daripada bateri AA atau AAA.Reka bentu...pada 1970/01/1 52199