CPLD menjelaskan: Panduan untuk peranti logik yang boleh diprogramkan

Dalam dunia reka bentuk elektronik yang dinamik, peranti logik yang boleh diprogramkan kompleks (CPLD) menonjol sebagai alat serba boleh, dengan lancar menggabungkan penyesuaian, ketepatan, dan kecekapan.Peranti ini merevolusikan reka bentuk litar dengan memperkenalkan sel -sel makro yang boleh diprogramkan dan matriks interkoneksi dominan, membolehkan penciptaan fungsi logik yang rumit dengan kebolehpercayaan yang luar biasa.Dari awal mereka pada tahun 1980 -an ke peranan utama mereka dalam industri moden seperti rangkaian, automotif, dan aeroangkasa, CPLD telah terbukti diperlukan untuk anda mencari fleksibiliti dan prestasi.Artikel ini menggali perjalanan CPLD, ciri tersendiri, aplikasi praktikal, dan metodologi pengaturcaraan yang menjadikan mereka asas dalam reka bentuk logik digital.Katalog

Gambaran keseluruhan CPLD

Di dalam penguasaan peranti logik yang boleh diprogramkan kompleks (CPLD), seseorang mendapati permaidani canggih sel -sel makro logik yang boleh diprogramkan, dihubungkan melalui matriks interkoneksi yang dominan.Garis unit makro (MC) dan input/output (I/O) ini membolehkan anda untuk membuat litar reka bentuk yang cekap, mengkonfigurasi struktur untuk fungsi yang unik.Tidak seperti peranti yang dibingungkan oleh masa interkoneksi rumit mereka, CPLD menggunakan wayar logam tak alih.Ciri -ciri ini memberikan kepada mereka tingkah laku jam yang konsisten dan boleh diramalkan, menjadikan ramalan masa lebih dipercayai dan tepat.

Perjalanan dan penggunaan

Tahun 1970 -an menyuarakan kedatangan peranti logik yang boleh diprogramkan (PLDS), memupuk langkah ke arah unit makro yang boleh diprogramkan.Peralihan ini memperkenalkan fleksibiliti reka bentuk yang mencukupi, membezakannya daripada litar digital statik, walaupun utiliti mereka pada mulanya dikekang ke litar yang lebih mudah.Kemunculan CPLD pada pertengahan 1980-an merevolusikan landskap ini, membuka jalan untuk reka bentuk litar kompleks.Sejak itu, mereka telah menenun diri ke dalam fabrik industri seperti rangkaian, elektronik automotif, pemesinan CNC, dan sistem aeroangkasa.Anda boleh mengenang tentang cara CPLDS mempermudah proses yang pernah menuntut buruh manual yang teliti, menandakan lonjakan yang luar biasa dalam kecekapan.

Kualiti CPLD tersendiri

CPLD membezakan diri mereka melalui pengaturcaraan yang boleh disesuaikan, integrasi yang luas, keupayaan pembangunan Swift, dan kebolehgunaan yang luas, bersama-sama dengan kos pengeluaran ekonomi.Mereka merayu kepada mereka yang mempunyai pengalaman perkakasan yang minimum, berfungsi sebagai produk yang boleh dipercayai dan selamat yang tidak memerlukan ujian menyeluruh.Sebagai bukti kehebatan mereka dalam reka bentuk litar berskala besar, CPLD memainkan peranan utama dalam pembangunan prototaip dan berkhidmat di bawah 10,000 unit, mewujudkan kecekapan yang berguna untuk anda.Ketepatan yang CPLD menyesuaikan diri dengan tuntutan projek yang berkembang sering memberi penghargaan kepada mereka, menekankan fleksibiliti sebenar mereka dalam persekitaran yang dinamik.

Kaedah permohonan

Litar bersepadu ini membolehkan anda menghuraikan fungsi logik yang disesuaikan dengan keperluan mereka menggunakan kedua -dua skema dan huraian perkakasan bahasa pada platform pembangunan.Sebagai contoh, dalam merancang mesin penjawab, skema, dan deskripsi perkakasan disediakan dan disusun pada komputer.Menggunakan kabel muat turun, kod dipindahkan ke CPLD untuk pengaturcaraan di sistem, yang terdiri daripada ujian, penyelesaian masalah, dan meningkatkan reka bentuk.Reka bentuk yang berjaya dibuat kemudiannya dihasilkan secara besar-besaran dengan mereplikasi cip CPLD.Dalam projek -projek seperti sistem lampu lalu lintas, mengulangi proses reka bentuk menjadi diperlukan, sama seperti membina semula rumah untuk memulihkan kebaruannya.Metodologi berulang ini sering meletakkan asas untuk menguasai, meningkatkan kemahiran dan keyakinan.

Varian utama

Selama bertahun -tahun, syarikat -syarikat seperti Altera, Lattice, dan Xilinx telah melancarkan garis -garis CPLD yang menonjol.Contoh yang perlu diperhatikan termasuk Altera EPM7128S, Kekisi LC4128V, dan Xilinx XC95108 .Model -model ini telah menemui peranan penting dalam pelbagai aplikasi global.Mereka yang mempunyai keistimewaan untuk bekerja dengan produk -produk yang berbeza ini sering menyatakan tentang perbezaan yang halus namun kuat yang mengoptimumkan fungsi tertentu.Ini mencerminkan proses pemilihan yang baik yang dipengaruhi oleh tuntutan projek tertentu, di mana setiap varian memegang rayuan uniknya.

Pengenalpastian dan klasifikasi FPGA dan CPLD

|

Aspek |

Cpld |

FPGA |

|

Pembentukan tingkah laku logik |

Bentuk tingkah laku logik menggunakan struktur jangka panjang produk.

Contoh: Siri ISPLSI Kekisi, Siri Xilinx XC9500, Altera Max7000S

Siri, Siri Lattice Mach |

Bentuk tingkah laku logik menggunakan kaedah carian jadual.

Contoh: Siri Xilinx Spartan, Altera Flex10k, Acex1k Siri |

|

Kesesuaian |

Sesuai untuk algoritma dan logik gabungan, berfungsi

Lebih baik dengan pencetus terhad dan istilah produk yang kaya |

Sesuai untuk logik berurutan, berfungsi dengan lebih baik

struktur yang kaya dengan pencetus |

|

Kelewatan masa |

Struktur pendawaian berterusan memberikan seragam dan

kelewatan masa yang boleh diramalkan |

Struktur pendawaian segmen membawa kepada masa yang tidak dapat diramalkan

kelewatan |

|

Fleksibiliti pengaturcaraan |

Litar dalaman tetap diubahsuai untuk pengaturcaraan.

Pengaturcaraan peringkat blok logik digunakan |

Pendawaian dalaman diubahsuai untuk pengaturcaraan.Logik

Pengaturcaraan peringkat pintu membolehkan fleksibiliti yang lebih besar |

|

Integrasi |

Integrasi yang lebih rendah berbanding dengan FPGA |

Integrasi yang lebih tinggi dengan struktur pendawaian yang lebih kompleks dan

pelaksanaan logik |

|

Kemudahan penggunaan |

Lebih mudah digunakan dengan pengaturcaraan melalui E2PROM atau FastFlash.

Tiada cip memori luaran diperlukan |

Memerlukan memori luaran untuk menyimpan pengaturcaraan

maklumat, yang membawa kepada penggunaan yang lebih kompleks |

|

Kelajuan dan kebolehprediksi |

Kelajuan yang lebih cepat dan kebolehprediksi masa yang lebih baik disebabkan oleh

interkoneksi lumped antara blok logik |

Kelajuan yang lebih perlahan dan masa yang kurang dapat diramal kerana

pengaturcaraan peringkat pintu dan interkoneksi diedarkan |

|

Teknologi pengaturcaraan |

Menggunakan pengaturcaraan memori E2PROM atau Flash.Data pengaturcaraan

dikekalkan apabila sistem itu dimatikan.Menyokong pengaturcaraan pada a

pengaturcara atau sistem |

Berdasarkan pengaturcaraan SRAM.Data pengaturcaraan hilang ketika

Sistem ini dimatikan dan mesti dimuat semula.Menyokong dinamik

konfigurasi |

|

Kerahsiaan |

Menawarkan kerahsiaan yang lebih baik |

Menyediakan kerahsiaan yang lebih rendah |

|

Penggunaan kuasa |

Penggunaan kuasa umum yang lebih tinggi, terutamanya dengan

integrasi yang lebih tinggi |

Penggunaan kuasa yang lebih rendah berbanding dengan CPLD |

Bahasa pengaturcaraan CPLD

Menganalisis bagaimana peranti logik yang boleh diprogramkan kompleks (CPLD) diprogramkan adalah asas dalam membuat penyelesaian perkakasan serba boleh.Kaedah sejarah untuk pengaturcaraan CPLD telah bergantung pada gambarajah tangga atau bahasa deskripsi perkakasan (HDLS), dengan Verilog HDL dan VHDL menjadi pilihan utama.Bahasa yang dipilih dapat membentuk kedua -dua strategi reka bentuk dan kecekapan operasi pelaksanaan.

• Verilog HDL: Verilog HDL dihargai untuk sintaks mudah dan keupayaan simulasi yang mantap, mencerminkan metodologi yang digunakan dalam reka bentuk logik digital.Integrasi dengan alat Automasi Reka Bentuk Elektronik (EDA) membolehkan anda melakukan sintesis dan simulasi dengan lancar.Sintaks C-seperti Verilog telah diperhatikan untuk menurunkan halangan untuk masuk bagi mereka yang mempunyai latar belakang pengaturcaraan, mempercepatkan perjalanan dari reka bentuk untuk digunakan di pelbagai sektor perindustrian.

• VHDL: VHDL menyediakan pilihan yang lebih rumit dan ekspresif untuk pengaturcaraan HDL.Selalunya pilihan untuk projek-projek yang menuntut dokumentasi yang teliti dan pemeriksaan jenis yang ketat, ciri-ciri yang dinilai dalam industri aeroangkasa dan pertahanan.Anda boleh perhatikan bahawa walaupun kerumitan berpotensi VHDL dalam projek yang lebih kecil, struktur disiplinnya menyokong penciptaan reka bentuk yang sangat dipercayai, keperluan dalam persekitaran di mana keselamatan dominan.

Tentang kita

ALLELCO LIMITED

Baca lebih lanjut

Siasatan Pantas.

Sila hantar pertanyaan, kami akan bertindak balas dengan segera.

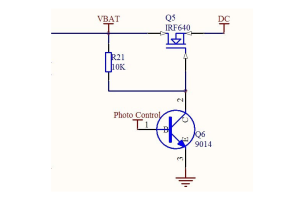

Transistor NMOS: Reka Bentuk, Operasi, dan Aplikasi

pada 2024/12/29

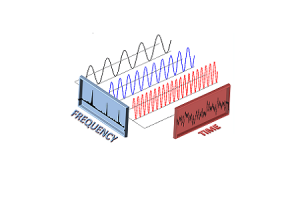

The Fast Fourier Transform (FFT): Merevolusi Pemprosesan Isyarat Digital

pada 2024/12/29

Jawatan popular

-

Arahan Kompleks Set Komputer: Bagaimana mereka menukar pengkomputeran?

pada 8000/04/19 147783

-

USB-C Pinout dan Ciri

pada 2000/04/19 112072

-

Menggunakan Primitif Simulasi Unified Xilinx: Panduan Komprehensif untuk Reka Bentuk dan Simulasi FPGA

pada 1600/04/19 111352

-

Voltan Bekalan Kuasa dalam Elektronik: Maksud VCC, VDD, VEE, VSS dan GND

pada 0400/04/19 83831

-

Panduan Penyambung RJ45: PINOUT, Pendawaian, Jenis Kabel, dan Kegunaan

pada 1970/01/1 79644

-

Panduan Terbaik untuk Kod Warna Kawat dalam Sistem Elektrik Moden

Cara sistem elektrik kita menggunakan warna bukan hanya untuk kelihatan.Setiap warna wayar kini menunjukkan fungsi tertentu, menjadikannya lebih mudah untuk mengenal pasti dan mengendalikan kompone...pada 1970/01/1 67010

-

Panduan Injap Purge: Fungsi, Gejala, Ujian, dan Penggantian Prestasi Enjin Optimal

Injap pembersihan adalah bahagian utama sistem kereta yang membantu menjaga udara bersih dengan menguruskan wap bahan api sebelum mereka dapat melarikan diri ke atmosfera.Ini bukan sahaja membantu ...pada 1970/01/1 63136

-

Faktor Kualiti (Q): Persamaan dan Aplikasi

Faktor kualiti, atau 'Q', adalah penting apabila memeriksa bagaimana induktor dan resonator berfungsi dalam sistem elektronik yang menggunakan frekuensi radio (RF).'Q' mengukur seberapa baik litar ...pada 1970/01/1 63067

-

Mencapai prestasi puncak dengan teorem pemindahan kuasa maksimum

Teorem pemindahan kuasa maksimum menerangkan bagaimana tenaga dari sumber, seperti bateri atau penjana, mengalir ke beban yang disambungkan.Ia menunjukkan keadaan yang tepat di mana beban menerima ...pada 1970/01/1 54099

-

Spesifikasi dan keserasian bateri A23

Bateri A23 adalah bateri berbentuk silinder kecil dengan voltan tinggi.Juga dipanggil 23A, 23AE, atau MN21, ia berjalan pada 12 volt dan lebih tinggi daripada bateri AA atau AAA.Reka bentu...pada 1970/01/1 52227